Что такое hub архитектура

Hub-архитектура

В новой серии 800 набора микросхем используется hub-архитектура, в которой компонент North Bridge получил название Memory Controller Hub (MCH), а компонент South Bridge —I/O Controller Hub (ICH). В результате соединения компонентов посредством шины PCI образуется стандартная конструкция North/South Bridge. В hub-архитектуре соединение компонентов выполняется с помощью выделенного hub-интерфейса, скорость которого вдвое выше скорости шины PCI. Hub-архитектура обладает некоторыми определенными преимуществами по отношению к традиционной конструкции North/South Bridge.

· Увеличенная пропускная способность. Hub-интерфейс представляет собой 8-разрядный интерфейс 4X (четырехтактный) с тактовой частотой 66 МГц (4?66 МГц? х 1 байт = 266 Мбайт/с), имеющий удвоенную по отношению к PCI пропускную способность (33 МГц? 32 байт =133 Мбайт/с).

· Уменьшенная загрузка PCI. Hub-интерфейс не зависит от PCI и не участвует в перераспределении или захвате полосы пропускания шины PCI при выполнении трафика набора микросхем или Super I/O. Это улучшает эффективность остальных устройств, подсоединенных к шине PCI, при выполнении групповых операций.

· Уменьшение монтажной схемы. Несмотря на удвоенную по сравнению с PCI пропускную способность, hub-интерфейс имеет ширину, равную 8 разрядам, и требует для соединения с системной платой всего лишь 15 сигналов. Шине PCI, например, для выполнения подобной операции требуется не менее 64 сигналов, что приводит к повышению генерации электромагнитных помех, ухудшению сигнала, появлению «шума» и в конечном итоге к увеличению себестоимости плат.

Конструкция hub-интерфейса предусматривает увеличение пропускной способности устройств PCI, что связано с отсутствием компонента South Bridge, передающего поток данных от микросхемы Super I/O и загружающего тем самым шину PCI. Таким образом, hub-архитектура позволяет увеличить пропускную способность устройств, непосредственно соединенных с I/O Controller Hub (ранее South Bridge), к которым относятся новые быстродействующие интерфейсы ATA-100 и USB 2.0.

Конструкция hub-интерфейса, ширина которого равна 8 бит, достаточно экономична. Ширина интерфейса может показаться недостаточной, но такая конструкция полностью себя оправдывает. При ширине интерфейса 8 бит достаточно только 15 сигналов, в то время как 32-разрядный интерфейс шины PCI, используемый в традиционной конструкции North/South Bridge, требует 64 сигналов. Меньшее число выводов говорит о более упрощенной схеме маршрутизации платы, снижении количества помех и повышении устойчивости сигнала. Это сокращает число выводов используемых микросхем, уменьшает их размеры и себестоимость.

Дата добавления: 2014-12-20 ; просмотров: 10 | Нарушение авторских прав

Hub-архитектура

| Название | Hub-архитектура |

| страница | 1/9 |

| Дата конвертации | 07.06.2013 |

| Размер | 483.82 Kb. |

| Тип | Документы |

| источник |

Hub-архитектура

Увеличенная пропускная способность.

Уменьшенная загрузка PCI.

Уменьшение монтажной схемы.

Hub-архитектура предусматривает увеличение пропускной способности устройств PCI, что связано с отсутствием компонента South Bridge, передающего поток данных от микросхемы Super I/O и загружающего тем самым шину PCI. Благодаря обходу PCI hub-архитектура позволяет увеличить пропускную способность устройств, непосредственно соединенных с I/O Controller Hub (ранее South Bridge), к которым относятся новые быстродействующие интерфейсы ATA-100 и USB 2.0

Архитектура системной платы

По мере «взросления» компьютеров постоянно расширяются функции чипсета системной платы и изменяются подходы к его построению. В задачу чипсетов для 80286/386 входили увязка шины процессора с относительно несложным контроллером памяти и подключение к этой связке шины (E)ISA, на которой располагались все устройства. Постепенно стала усложняться подсистема памяти — появился кэш на системной плате, а потом к нему добавился встроенный кэш процессора. Для процессоров класса 486 производительности шины (E)ISA оказалось уже недостаточно, и появились новые шины. Шина VLB, как просто физически оформленная разъемом системная шина процессора класса 486, особых хлопот чипсету не доставляла. Однако появилась шина PCI, для которой пришлось строить мост от системной шины. Поначалу ее называли «пристроечной» (mezzanine bus), но вскоре она надолго стала центральной шиной, вокруг которой компоновались все остальные элементы. Ее центральное место не оспаривалось, поскольку шина PC имела высокую производительность — 132 Мбайт/с. Традиционно на схемах шину PCI изображают посередине, как экватор. Процессор и память (вместе с кэш-памятью) изображают выше — «севернее», а шину ISA и все устройства, подключаемые к PCI и ISA, изображают ниже — «южнее экватора». Соответствующие части чипсета получили укоренившиеся названия северных (north) и южных (south). Созвучное слово «серверный» относится к чипсету, ориентированному на применение в компьютерах-серверах.

Шинно-мостовая архитектура

В шинно-мостовой архитектуре имеется центральная магистральная шина, к которой остальные компоненты подключаются через мосты. В роли центральной магистрали сначала выступала шина (E)ISA, затем ее сменила шина PCI. Шинно-мостовая архитектура чипсетов просуществовала долгое время и пережила много поколений процессоров (от 2-го до 7-го). Перемещение вторичного кэша с системной платы на процессор (Р6 и Pentium 4 у Intel и К7 у AMD) несколько упростило северную часть чипсета — в ней не надо управлять статической кэш-памятью, а остается лишь обеспечивать когерентность процессорного кэша с основной памятью, доступ к которой возможен и со стороны шины PCI.

Шина PCI в роли главной магистрали удержалась недолго: видеокартам с ЗD-акселератором ее пропускной способности, разделяемой между всеми устройствами, оказалось недостаточно. Тогда и появился порт AGP как выделенный мощный интерфейс между графическим акселератором и памятью (а также процессором). При этом задачи северного моста усложнились: контроллеру памяти приходится работать уже на три фронта — ему посылают запросы процессор, мастера шины PCI (и ISA, но тоже через PCI) и порт AGP. Пропускная способность AGP в режиме 2х/4х/8х составляет 533/1066/2133 Мбайт/с, так что шина PCI по производительности стала уже второстепенной. Однако в шинно-мостовой архитектуре она сохраняет свою роль магистрали подключения всех периферийных устройств (кроме графических). В качестве мощного представителя шинно-мостовой архитектуры можно рассматривать чипсет AMD-760. Здесь имеются первичная шина PCI на 64 бит и 66 МГц, являющаяся «экватором», и вторичная шина для подключения рядовой периферии.

Шина, к которой подключается множество устройств, является узким местом по ряду причин. Во-первых, из-за большого числа устройств, подключенных (электрически) к шине, не удается поднять тактовую частоту до уровня, достижимого в двухточечных соединениях. Во-вторых, шина, к которой подключается множество разнотипных устройств (особенно расположенных на картах расширения), обременена грузом обратной совместимости со старыми периферийными устройствами. Например, предусмотренные возможности повышения производительности PCI используются не всегда: расширение разрядности до 64 бит обходится слишком дорого (большое число проводников порождает свои проблемы), а повышение частоты до 66 МГц для шины возможно лишь если все ее абоненты поддерживают эту частоту. Достаточно установить одну «простую» карту PCI, и производительность центральной шины падает до начальных 133 Мбайт/с. То же можно сказать и о PCI-X: достаточно подключить к ней одно устаревшее устройство PCI, и все протокольные усовершенствования будут отменены.

Хабовая архитектура

С введением высокоскоростных режимов UltraDMA (ATA/66, ATA/100, а затем и AT А/133) связь двухканального контроллера IDE с памятью через шину PCI стала уже слишком сильно нагружать эту шину. Кроме того, появились высокоскоростные интерфейсы Gigabit Ethernet, FireWire (100/200/400/800 Мбит/с) и USB 2.0 (480 Мбит/с). Ответом на эти изменения в расстановке сил стал переход на хабовую архитектуру чипсета. В данном контексте хабы — это специализированные микросхемы, обеспечивающие передачу данных между своими внешними интерфейсами. Этими интерфейсами являются «прикладные» интерфейсы подключения процессоров, модулей памяти, шин расширения и периферийные интерфейсы (ATA, SATA, USB, FireWire, Ethernet). Поскольку к одной микросхеме все эти интерфейсы не подключить (слишком сложна структура и много требуется выводов), чипсет строится, как правило, из пары основных хабов (северного и южного), связанных между собой высокопроизводительным каналом.

Северный хаб чипсета выполняет те же функции, что и северный мост шинно-мостовой архитектуры: он связывает шины процессора, памяти и порта AGP. Однако на южной стороне этого хаба находится уже не шина PCI, а высокопроизводительный интерфейс связи с южным хабом. Пропускная способность этого интерфейса составляет 266 Мбайт/с и выше, в зависимости от чипсета. Если чипсет имеет интегрированную графику, то в северный хаб входит и графический контроллер со всеми своими интерфейсами (аналоговыми и цифровыми интерфейсами дисплея, шиной локальной памяти). Чипсеты с интегрированным графическим контроллером могут иметь внешний порт AGP, который становится доступным при отключении встроенного графического контроллера. Есть чипсеты, у которых порт AGP является чисто внутренним средством соединения встроенного контроллера, и внешний графический контроллер к ним может подключаться только по шине PCI.

С появлением PCI-E архитектура не слишком изменилась: северный хаб (мост) вместо порта AGP теперь предлагает высокопроизводительный (8х или 16х) порт, а то и пару портов PCI-E для подключения графического адаптера. Маломощные (1х) порты PCI-E могут предоставляться как северным, так и южным хабами (это решает разработчик чипсета). В последнем случае корневой комплекс PCI-E «расползается» по двум микросхемам чипсета, связанным между собой «фирменным» интерфейсом. Использования PCI-E как единой коммуникационной базы внутри чипсета пока не наблюдается.

Архитектура HyperTransport

Технология (архитектура) HyperTransport (HT) задумывалась как альтернатива шинно-мостовой архитектуре системных плат. Технология разработана компаниями AMD, Apple Computers, Broadcom, Cisco Systems, NVIDIA, PMC-Sierra, SGI, SiPackets, Sun Microsystems, Transmeta. Первый релиз вышел в 2001 году, в 2003-м — версия 1.10. Прежнее кодовое название — LDT (Lighting Data Transport).

Основная идея НТ — замена шинного соединения компонентов (периферийных устройств) системой двухточечных встречно направленных соединений. При этом достижима более высокая тактовая частота интерфейсов, что обеспечивает их более высокую (по сравнению с шиной) пропускную способность. Главный мост (host bridge) обеспечивает связь НТ с ядром — процессором и памятью. Периферийные контроллеры, требующие высокой пропускной способности, реализуются в виде НТ-туннелей. В архитектуре предусматривается и мостовая связь с шиной PCI.

Архитектура НТ обеспечивает все типы транзакций процессоров и устройств PCI, PCI-X и AGP, используемые в PC. Транзакции выполняются в виде серий передач пакетов различных типов. В традиционных транзакциях целевое устройство идентифицируется адресом: чтение и запись в пространстве памяти, ввод-вывод в конфигурационном пространстве, а также считывание вектора прерывания из PIC 8259A и специальные циклы PCI. Для унификации транзакций все пространства отображаются на единое 40-битное пространство адресов (объем 1 Тбайт), адрес передается в управляющих пакетах. Первые 1012 Гбайт пространства выделены для отображения обычного пространства памяти (для ОЗУ и ввода-вывода, отображенного на память). В оставшейся 12-гигабайтной области размещаются конфигурационное пространство (32 Мбайт), пространство ввода-вывода (32 Мбайт), память SMM, пространства адресов для выдачи векторов и подтверждения прерываний; 54 Мбайт остались в резерве. Транзакции НТ обеспечивают программное взаимодействие процессора с устройствами, прямой доступ к памяти и одноранговое взаимодействие устройств с адресацией в описанном комбинированном пространстве. Существует сетевое расширение спецификации, поддерживающее обмен сообщениями (как в сетях), причем возможны и широковещательные сообщения.

Транзакции выполняются расщепленным способом: инициатор посылает пакет-запрос и данные для транзакции записи, целевое устройство посылает пакет-ответ и данные для транзакций чтения. Технология НТ обеспечивает упорядоченность выполнения транзакций; есть возможность регулировать качество обслуживания (Quality of Service, QoS), что позволяет организовывать изохронные передачи.

Сигнализация прерываний в НТ реализуется тоже пакетами: устройство посылает сообщение — выполняет транзакцию записи по адресу, указанному ему при конфигурировании (аналогично MSI на шине PCI). Обработчик прерывания посылает сообщение о завершении обработки прерывания (End Of Interrupt, EOI), делая запись по другому адресу, связанному с данным устройством. Такой механизм сигнализации запросов и подтверждений позволяет преодолеть неэффективность традиционого для PC механизма прерываний с помощью специальных линий IRQ.

Возможны и более сложные топологии, например дерево (с мостами), позволяющее подключать больше тупиковых устройств. Возможна и цепочка с двумя хостами (на обоих концах), которая может использоваться двояко. В первом варианте обеспечиваются избыточность (дублирование функций хоста) и разделяемость узлов (доступность обоим хостам). При этом один главный мост становится ведущим («настоящим», разворачивающим одноранговые запросы и ответы), через него обеспечивается конфигурирование узлов. Другой мост становится ведомым — он является лишь средством связи второго хоста (процессора) с узлами. Программно при конфигурировании (инициализации НТ) роли мостов можно поменять. Во втором варианте одно из устройств разбивает шину (перестает работать туннелем), в результате получаются два хоста со своими короткими цепочками собственных (неразделяемых) устройств. С применением коммутаторов можно строить и более сложные, но беспетлевые топологии.

Помимо сигналов для передачи пакетов, имеются сигналы сброса и инициализации (PWR0K — признак стабильности питания и синхронизации, RESET# — сброс цепочки устройств), а также управления энергопотреблением (LDTST0P# — разрешение/запрет использования соединения при смене состояний системы, LDTREQ# — индикатор активности соединения или его запроса устройством). Эти сигналы «медленные», их формируют передатчики с открытым стоком (open-drain), все одноименные сигналы цепочки объединяются, выполняя функцию «монтажного ИЛИ». Уровни сигналов — LVTTL/CMOS (2,4 В).

По замыслу разработчиков, НТ должна стать архитектурой построения PC, однако пока что используется лишь технология НТ. В вышеприведенном примере главный мост реализует интерфейс AGP. В 64-битных процессорах AMD, в которых применяется НТ, главный мост размещается в самом процессоре. При этом у процессора оказывается два интерфейса: интерфейс памяти (пока что DDR SDRAM) и НТ в качестве системной шины. В распространенных чипсетах (от VIA, SiS) к интерфейсу НТ подключается только северный хаб, обеспечивающий лишь интерфейс подключения графического адаптера — AGP или PCI-E. Южный хаб соединяется с северным собственным интерфейсом, так что использования НТ как универсальной транспортной структуры для множества компонентов пока не наблюдается.

Северные мосты и хабы

Северный мост определяет также поддерживаемые частоты и разрядность шины PCI и PCI-X, возможное количество контроллеров шины PCI (число пар сигналов арбитра PCI), способы буферизации, возможности одновременных обменов. Северный хаб на эти параметры уже не влияет, поскольку шины PCI и PCI-X подключаются к южному хабу.

Южные мосты и хабы

Южный хаб чипсета обеспечивает подключение шин PCI, PCI-X и «маломощных» портов PCI-E, ISA (но уже не всегда), АТА (2 канала), SATA, USB, FireWire, а также «мелких» контроллеров ввода-вывода, памяти CMOS и флэш-памяти с системным модулем BIOS. В южной части располагаются таймер (8254), контроллер прерываний (совместимый с парой 8259 или APIC), контроллер DMA для шины ISA и периферии системной платы. Если в чипсет интегрирован звук, то южный хаб (мост) имеет контроллер интерфейса AC-Link или HDA Link для подключения аудиокодека, а то и сам аудиокодек. Поскольку шина ISA отправляется в отставку, для контроллеров ввода-вывода, ранее подключавшихся к шине X-BUS (это практически та же ISA), ввели новый интерфейс LPC (Low Pin Count). Он, как и следует из названия, имеет малое число линий [6], что значительно облегчает разработку чипсета и системной платы. Флэш-память для хранения системной памяти BIOS стали помещать в специальный хаб (firmware hub), соединяемый с южным хабом отдельной шиной (аналогичной LPC). Флэш-память может подключаться и прямо к шине LPC. Для подключения энергонезависимой памяти (EEPROM) хаб может иметь дополнительный последовательный интерфейс. Для обслуживания процессоров, имеющих дополнительную сервисную шину SMBus, а также для поддержки слота CNR хаб может иметь последовательный интерфейс I2C (Inter 1С — интерфейс связи микросхем). Этот же интерфейс может использоваться для чтения идентификаторов модулей памяти. В южный хаб интегрированных чипсетов вводят и контроллер локальной сети (как правило, Ethernet).

Логически южный хаб представляется как набор виртуальных мостов и устройств, подключенных к главной шине PCI. Однако обмены данными с широкополосными устройствами (IDE, SATA, USB, FireWire, Ethernet, AC’97 или HDA) на внешнюю шину PCI все-таки не «выплескивают», иначе теряется смысл южного хаба.

Синхронизация и потоки данных

Как видно, в чипсете обеспечивается взаимодействие множества шин, большинство которых синхронные. Вопросы синхронизации решаются по-разному. У чипсетов для шины Pentium память всегда работала на частоте системной шины (60-100 МГц), а частота шины PCI (номинал 33 МГц) была к ней привязана с коэффициентом 1:2 или 1:3. При частоте системной шины, отличной от 66 или 100 МГц, шина PCI оказывалась либо разогнанной, либо приторможенной.

В чипсетах с портом AGP частоту шины памяти стремятся повысить, иначе память становится узким местом: к ней обращаются акселератор с AGP, ведущие устройства PCI и, наконец, сам процессор. При этом у процессора может быть частота шины всего 66 МГц (как, например, у процессоров Celeron). Для любителей разгонов полезно такое свойство чипсетов, как асинхронностъ — возможность относительно произвольного задания частот системной шины, шины памяти, порта AGP, шины PCI. Заметим, что частота шин LPC и шины подключения хаба с BIOS (FWH) совпадает с частотой PCI (33 МГц), и разгон шины PCI влечет за собой разгон и этих шин, однако поведение их абонентов на повышенных частотах может огорчить пользователя невозможностью разгона. Конечно же, здесь асинхронность условна — опорный генератор все-таки один, но коэффициенты для каждого домена синхронизации (группы тесно связанных узлов) задаются раздельно. Таким образом, можно из всех компонентов «выжать» максимум производительности. Однако при определенных соотношениях частот компонентов (как правило, не равных степени двойки) из-за промежуточной буферизации данных наблюдается снижение суммарной производительности системы.

Чипсеты и платы

Хотя чипсеты в значительной степени определяют свойства системных плат, выполненных на их основе, у разработчика плат всегда остаются возможности упростить плату и «испортить хорошую вещь». Так что системные платы, выполненные на одном и том же чипсете, могут иметь разные характеристики по производительности и разный диапазон поддерживаемых устанавливаемых компонентов (процессоров, памяти, интерфейса). И, конечно же, существенную роль в реализации всех полезных свойств чипсета играют BIOS и применяемые версии системных драйверов. Чипсеты ориентируются на разные применения системных плат, и функции, необходимые для сервера, могут оказаться лишними для офисного компьютера, а за излишества всегда приходится платить. Поэтому нельзя чипсеты выстроить по порядку от худшего к лучшему, они позиционируются в многомерном пространстве противоречивых требований. Сравнивать интегрированные чипсеты нужно не только по общим параметрам, но и по характеристикам графики, звука, адаптера локальной сети. Основные параметры распространенных системных плат (и чипсетов) приведены в литературе. Результаты тестирования и сравнения системных плат регулярно публикуются в периодических изданиях.

Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

Системные платы

Наборы микросхем системной логики

Архитектура ‘‘северный/южный мост’’

Большинство ранних версий наборов микросхем Intel (и практически все наборы микросхем других производителей) созданы на основе многоуровневой архитектуры и содержат следующие компоненты: северный мост, южный мост и микросхему Super I/O.

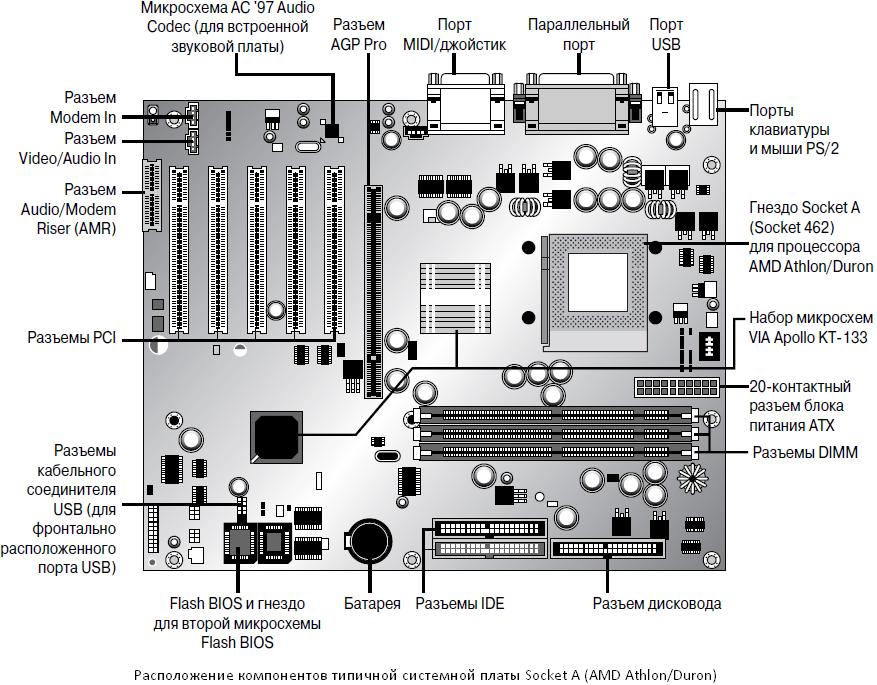

Расположение всех микросхем и компонентов типичной системной платы AMD Socket A, использующей архитектуру “северный/южный мост”, показано на рис. 4.30. Северный мост иногда называют контроллером PAC (PCI/AGP Controller). В сущности, он является основным компонентом системной платы и единственной, за исключением процессора, схемой, работающей на полной частоте системной платы (шины процессора). В современных наборах микросхем используется однокристальная микросхема северного моста; в более ранних версиях содержалось до трех отдельных микросхем, составляющих полную схему северного моста.

Южный мост обладает более низким быстродействием и всегда находится на отдельной микросхеме. Одна и та же микросхема южного моста может использоваться в различных наборах микросхем системной логики. (Разные типы схем северного моста, как правило, разрабатываются с учетом того, чтобы можно было использовать один и тот же компонент южного моста.) Благодаря модульной конструкции набора микросхем системной логики стало возможным снизить стоимость и расширить поле деятельности для изготовителей системных плат. Южный мост подключается к шине PCI (33 МГц) и содержит интерфейс шины ISA (8 МГц). Кроме того, обычно он содержит две схемы, реализующие интерфейс контроллера жесткого диска IDE и интерфейс USB (Universal Serial Bus — универсальная последовательная шина), а также схемы, реализующие функции памяти CMOS и часов. В старых конструкциях южный мост содержал также все компоненты, необходимые для шины ISA, включая контроллер прямого доступа к памяти и контроллер прерываний.

Микросхема Super I/O, которая является третьим компонентом системной платы, соединена с шиной ISA (8 МГц) и содержит все стандартные периферийные устройства, встроенные в системную плату. Например, большинство микросхем Super I/O поддерживают параллельный порт, два последовательных порта, контроллер гибких дисков, интерфейс “клавиатура/мышь”. К числу дополнительных компонентов могут быть отнесены CMOS RAM/Clock, контроллеры IDE, а также интерфейс игрового порта. Системы, содержащие порты IEEE-1394 и SCSI, используют для портов этого типа отдельные микросхемы.

В новых системных платах с микросхемами северного и южного мостов представлена микросхема Super-South Bridge, которая включает в себя функциональные возможности сразу двух микросхем — собственно южного моста и Super I/O.

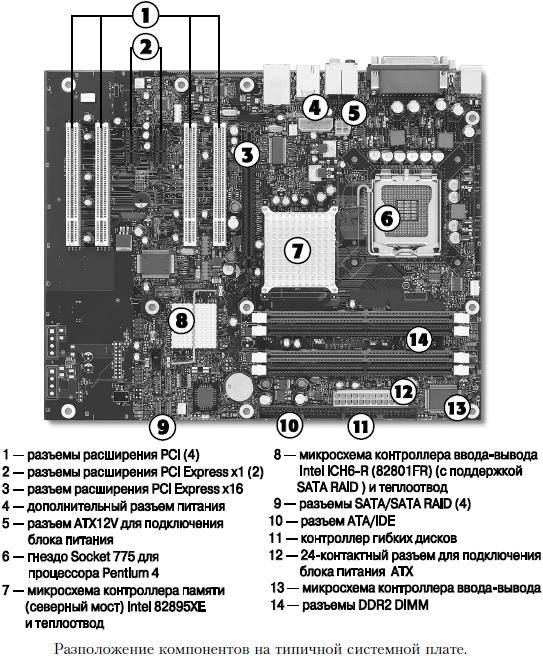

Hub-архитектура

Новые наборы микросхем системной логики от Intel используют архитектуру концентратора (hub-архитектуру), в которой бывший северный мост называется концентратором контроллера памяти (Memory Controller Hub — MCH), а южный — концентратором контроллера ввода-вывода (I/O Controller Hub — ICH). Системы с интегрированной графикой вместо стандартного MCH используют концентратор контроллера графической памяти (Graphics Memory Controller Hub — GMCH).

Вместо соединения этих контроллеров через шину PCI, как в стандартной архитектуре “северный/южный мост”, взаимодействие между ними осуществляется через выделенный интерфейс концентратора, быстродействие которого вдвое выше, чем быстродействие PCI. Hub-архитектура обладает определенными преимуществами по сравнению с традиционной архитектурой “северный/южный мост”.

Существует два основных варианта интерфейса концентратора.

Конструкция hub-интерфейса, ширина которого равна 4 или 8 бит, довольно экономична. Ширина интерфейса может показаться недостаточной, но такая конструкция полностью себя оправдывает. Меньшее число выводов говорит об упрощенной схеме маршрутизации платы, снижении количества помех и повышении устойчивости сигнала. Это также сокращает число выводов используемых микросхем, уменьшает их размеры и себестоимость. Таким образом, посредством очень узкой, но быстродействующей архитектуры интерфейс концентратора достигает высших показателей быстродействия, чем те, на которые была способна старая архитектура “северный/южный мост”.

Кроме того, в ICH содержится новая шина Low-Pin-Count (LPC), представляющая собой 4-разрядную версию шины PCI, которая была разработана, в первую очередь, для поддержки микросхем системной платы ROM BIOS и Super I/O. Вместе с четырьмя сигналами функций данных, адресов и команд для функционирования шины требуется девять дополнительных сигналов, что составляет в общей сложности 13 сигналов. Это позволяет значительно уменьшить количество линий, соединяющих ROM BIOS с микросхемами Super I/O. Для сравнения: в ранних версиях наборов микросхем в качестве интерфейса между северным и южным мостами использовалась шина ISA, количество сигналов которой равно 98. Максимальная пропускная способность шины LPC достигает 16,67 Мбайт/с, что примерно соответствует параметрам ISA и чего более чем достаточно для поддержки таких устройств, как ROM BIOS и микросхемы Super I/O.

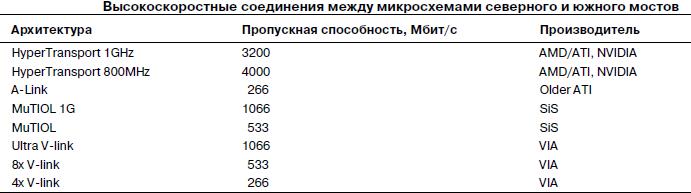

Высокоскоростные соединения между микросхемами северного и южного мостов

Intel — не единственная компания, которая стремится заменить медленное соединение по шине PCI между микросхемами северного и южного мостов более производительной альтернативой, не основанной на шине PCI. Ниже описываются подобные архитектуры, созданные несколькими компаниями.

Технические характеристики наборов микросхем от разных производителей представлены в таблице ниже.

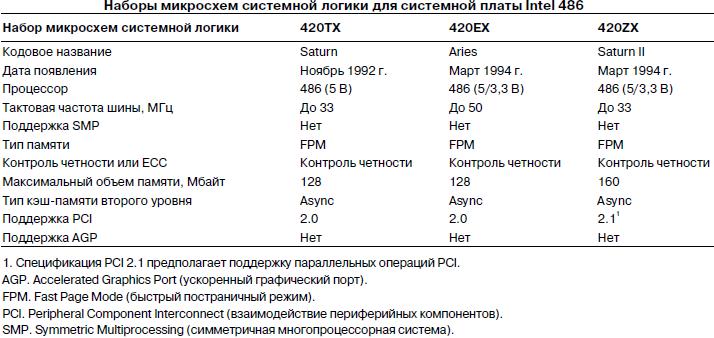

Первые наборы микросхем системной логики 386/486 компании Intel

Первый набор микросхем системной логики 82350 предназначался для процессоров 386DX и 486. Но он успеха не имел, так как шина EISA не получила широкого распространения, к тому же многие производители выпускали наборы микросхем для этих процессоров. Однако ситуация на рынке постоянно изменялась, Intel отказалась от поддержки шины EISA, и последующие наборы микросхем системной логики для процессора 486 были намного удачливее.

В таблице ниже перечислены наборы микросхем системной логики для процессора Intel 486.

В наборе микросхем 420 впервые была представлена архитектура “северный/южный мост”, которая продолжает использоваться в некоторых моделях и по сей день.

Пятое поколение микросхем системной логики Pentium (P5)

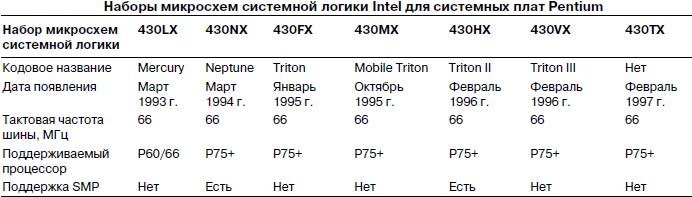

Одновременно с процессором Pentium в марте 1993 года Intel представила свой первый набор микросхем системной логики 430LX (под кодовым названием Mercury) для Pentium. Именно в этот год Intel серьезно занялась проектированием наборов микросхем системной логики и приложила все усилия, чтобы стать лидером на рынке. И поскольку у других производителей на проектирование наборов микросхем системной логики уходило несколько месяцев, а то и год, Intel очень скоро добилась своей цели. В табл. 4.14 перечислены наборы микросхем системной логики Intel для системных плат Pentium. Обратите внимание, что один из них не поддерживает порты AGP — эта поддержка была добавлена только в наборы микросхем, предназначенные для процессоров семейства Pentium II/Celeron.

Примечание!

Стандарт PCI 2.1 поддерживает параллельное выполнение операций на шине PCI.

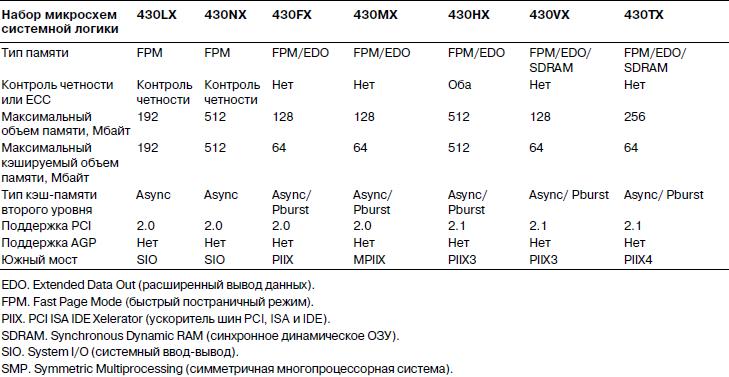

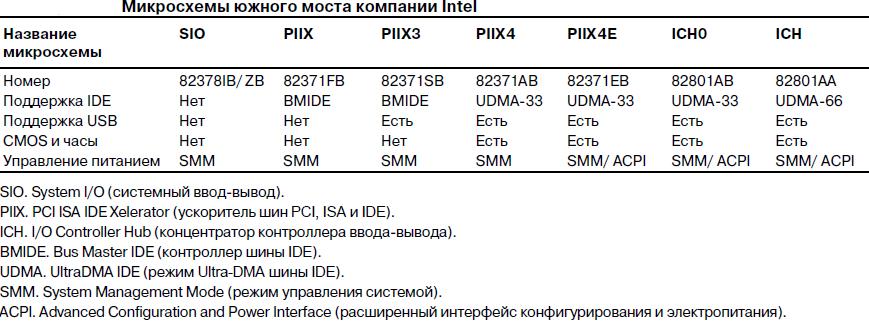

В таблице ниже перечислены все микросхемы южного моста, составляющие вторую часть наборов микросхем системной логики пятого поколения процессоров на системных платах Intel.

Наборы микросхем для процессоров Pentium, перечисленные в таблицах, не выпускаются уже на протяжении нескольких лет. Основная часть компьютеров, в которых они использовались, уже давно находится на “свалке истории”.

Толчком к созданию наборов микросхем системной логики класса, отличного от Pentium, послужила разработка компанией AMD собственных аналогов Pentium — процессоров семейств K5 и K6. Процессор K5 не достиг больших успехов; в отличие от него процессоры семейства K6 заняли доминирующее положение на рынке недорогих систем, а также стали использоваться для модернизации систем Pentium. Компания AMD чаще использует компоненты сторонних производителей, чем собственные наборы микросхем. Но возможность своевременной поставки соответствующих наборов микросхем, позволяющих поддерживать продукты AMD, сделала процессор K6 и его наследников наиболее вероятными конкурентами процессоров семейств Intel Pentium MMX и Pentium II/III/Celeron. Эта же возможность подтолкнула других поставщиков, таких как VIA, Acer Laboratories и SiS, к поддержке процессоров AMD. К наиболее распространенным наборам микросхем для процессоров класса Pentium относятся следующие: