Что значит регистровая память

Про ранги и виртуализацию в RAM

В продолжение рубрики «конспект админа» хотелось бы разобраться в нюансах технологий ОЗУ современного железа: в регистровой памяти, рангах, банках памяти и прочем. Подробнее коснемся надежности хранения данных в памяти и тех технологий, которые несчетное число раз на дню избавляют администраторов от печалей BSOD.

Старые песни про новые типы

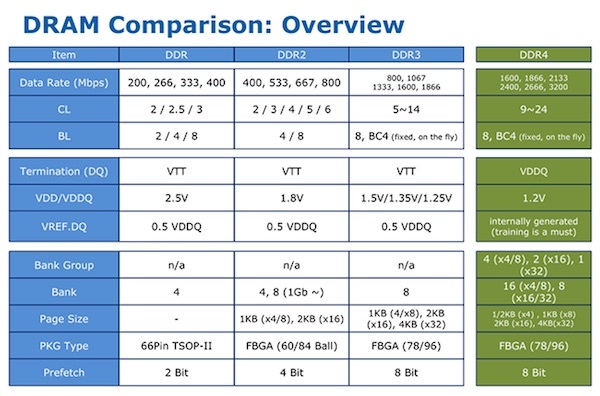

Сегодня на рынке представлены, в основном, модули с памятью DDR SDRAM: DDR2, DDR3, DDR4. Разные поколения отличаются между собой рядом характеристик – в целом, каждое следующее поколение «быстрее, выше, сильнее», а для любознательных вот табличка:

Для подбора правильной памяти больший интерес представляют сами модули:

RDIMM — регистровая (буферизованная) память. Удобна для установки большого объема оперативной памяти по сравнению с небуферизованными модулями. Из минусов – более низкая производительность;

UDIMM (unregistered DRAM) — нерегистровая или небуферизованная память — это оперативная память, которая не содержит никаких буферов или регистров;

LRDIMM — эти модули обеспечивают более высокие скорости при большей емкости по сравнению с двухранговыми или четырехранговыми модулями RDIMM, за счёт использования дополнительных микросхем буфера памяти;

HDIMM (HyperCloud DIMM, HCDIMM) — модули с виртуальными рангами, которые имеют большую плотность и обеспечивают более высокую скорость работы. Например, 4 физических ранга в таких модулях могут быть представлены для контроллера как 2 виртуальных;

Попытка одновременно использовать эти типы может вызвать самые разные печальные последствия, вплоть до порчи материнской платы или самой памяти. Но возможно использование одного типа модулей с разными характеристиками, так как они обратно совместимы по тактовой частоте. Правда, итоговая частота работы подсистемы памяти будет ограничена возможностями самого медленного модуля или контроллера памяти.

Для всех типов памяти SDRAM есть общий набор базовых характеристик, влияющий на объем и производительность:

частота и режим работы;

Конечно, отличий на самом деле больше, но для сборки правильно работающей системы можно ограничиться этими.

Частота и режим работы

Понятно, что чем выше частота — тем выше общая производительность памяти. Но память все равно не будет работать быстрее, чем ей позволяет контроллер на материнской плате. Кроме того, все современные модули умеют работать в в многоканальном режиме, который увеличивает общую производительность до четырех раз.

Режимы работы можно условно разделить на четыре группы:

Single Mode — одноканальный или ассиметричный. Включается, когда в системе установлен только один модуль памяти или все модули отличаются друг от друга. Фактически, означает отсутствие многоканального доступа;

Dual Mode — двухканальный или симметричный. Слоты памяти группируются по каналам, в каждом из которых устанавливается одинаковый объем памяти. Это позволяет увеличить скорость работы на 5-10 % в играх, и до 70 % в тяжелых графических приложениях. Модули памяти необходимо устанавливать парами на разные каналы. Производители материнских плат обычно выделяют парные слоты одним цветом;

Triple Mode — трехканальный режим работы. Модули устанавливаются группами по три штуки — на каждый из трех каналов. Аналогично работают и последующие режимы: четырехканальные (quad-channel), восьмиканальные (8-channel memory) и т.п.

Для максимального быстродействия лучше устанавливать одинаковые модули с максимально возможной для системы частотой. При этом используйте установку парами или группами — в зависимости от доступного многоканального режима работы.

Ранги для памяти

Ранг (rank) — область памяти из нескольких чипов памяти в 64 бита (72 бита при наличии ECC, о чем поговорим позже). В зависимости от конструкции модуль может содержать один, два или четыре ранга.

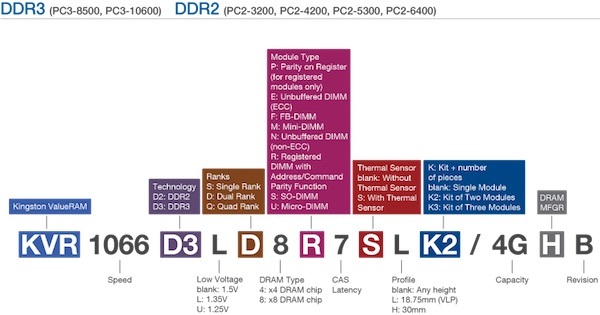

Узнать этот параметр можно из маркировки на модуле памяти. Например уKingston число рангов легко вычислить по одной из трех букв в середине маркировки: S (Single — одногоранговая), D (Dual — двухранговая), Q (Quad — четырехранговая).

Пример полной расшифровки маркировки на модулях Kingston:

Серверные материнские платы ограничены суммарным числом рангов памяти, с которыми могут работать. Например, если максимально может быть установлено восемь рангов при уже установленных четырех двухранговых модулях, то в свободные слоты память добавить не получится.

Перед покупкой модулей есть смысл уточнить, какие типы памяти поддерживает процессор сервера. Например, Xeon E5/E5 v2 поддерживают одно-, двух- и четырехранговые регистровые модули DIMM (RDIMM), LRDIMM и не буферизированные ECC DIMM (ECC UDIMM) DDR3. А процессоры Xeon E5 v3 поддерживают одно- и двухранговые регистровые модули DIMM, а также LRDIMM DDR4.

Немного про скучные аббревиатуры таймингов

Тайминги или латентность памяти (CAS Latency, CL) — величина задержки в тактах от поступления команды до ее исполнения. Числа таймингов указывают параметры следующих операций:

CL (CAS Latency) – время, которое проходит между запросом процессора некоторых данных из памяти и моментом выдачи этих данных памятью;

tRCD (задержка от RAS до CAS) – время, которое должно пройти с момента обращения к строке матрицы (RAS) до обращения к столбцу матрицы (CAS) с нужными данными;

tRP (RAS Precharge) – интервал от закрытия доступа к одной строке матрицы, и до начала доступа к другой;

tRAS – пауза для возврата памяти в состояние ожидания следующего запроса;

Разумеется, чем меньше тайминги – тем лучше для скорости. Но за низкую латентность придется заплатить тактовой частотой: чем ниже тайминги, тем меньше допустимая для памяти тактовая частота. Поэтому правильным выбором будет «золотая середина».

Существуют и специальные более дорогие модули с пометкой «Low Latency», которые могут работать на более высокой частоте при низких таймингах. При расширении памяти желательно подбирать модули с таймингами, аналогичными уже установленным.

RAID для оперативной памяти

Ошибки при хранении данных в оперативной памяти неизбежны. Они классифицируются как аппаратные отказы и нерегулярные ошибки (сбои). Память с контролем четности способна обнаружить ошибку, но не способна ее исправить.

Для коррекции нерегулярных ошибок применяется ECC-память, которая содержит дополнительную микросхему для обнаружения и исправления ошибок в отдельных битах.

Метод коррекции ошибок работает следующим образом:

При записи 64 бит данных в ячейку памяти происходит подсчет контрольной суммы, составляющей 8 бит.

Когда процессор считывает данные, то выполняется расчет контрольной суммы полученных данных и сравнение с исходным значением. Если суммы не совпадают – это ошибка.

Технология Advanced ECC способна исправлять многобитовые ошибки в одной микросхеме, и с ней возможно восстановление данных даже при отказе всего модуля DRAM.

Исправление ошибок нужно отдельно включить в BIOS

Большинство серверных модулей памяти являются регистровыми (буферизованными) – они содержат регистры контроля передачи данных.

Регистры также позволяют устанавливать большие объемы памяти, но из-за них образуются дополнительные задержки в работе. Дело в том, что каждое чтение и запись буферизуются в регистре на один такт, прежде чем попадут с шины памяти в чип DRAM, поэтому регистровая память оказывается медленнее не регистровой на один такт.

Все регистровые модули и память с полной буферизацией также поддерживают ECC, а вот обратное не всегда справедливо. Из соображений надежности для сервера лучше использовать регистровую память.

Многопроцессорные системы и память

Для правильной и быстрой работы нескольких процессоров, нужно каждому из них выделить свой банк памяти для доступа «напрямую». Об организации этих банков в конкретном сервере лучше почитать в документации, но общее правило такое: память распределяем между банками поровну и в каждый ставим модули одного типа.

Если пришлось поставить в сервер модули с меньшей частотой, чем требуется материнской плате – нужно включить в BIOS дополнительные циклы ожидания при работе процессора с памятью.

Для автоматического учета всех правил и рекомендаций по установке модулей можно использовать специальные утилиты от вендора. Например, у HP есть Online DDR4 (DDR3) Memory Configuration Tool.

Итого

Вместо пространственного заключения приведу общие рекомендации по выбору памяти:

Для многопроцессорных серверов HP рекомендуется использовать только регистровую память c функцией коррекции ошибок (ECC RDIMM), а для однопроцессорных — небуферизированную с ECC (UDIMM). Планки UDIMM для серверов HP лучше выбирать от этого же производителя, чтобы избежать самопроизвольных перезагрузок.

В случае с RDIMM лучше выбирать одно- и двухранговые модули (1rx4, 2rx4). Для оптимальной производительности используйте двухранговые модули памяти в конфигурациях 1 или 2 DIMM на канал. Создание конфигурации из 3 DIMM с установкой модулей в третий банк памяти значительно снижает производительность.

Список короткий, но здесь все самое необходимое и наименее очевидное. Конечно же, старый как мир принцип RTFM никто не отменял.

Registered DIMM: основные моменты

Как известно, одним из самых главных требований к модулю памяти (впрочем, как и к любому другому устройству) является максимальная отказоустойчивость стабильное функционирование без сбоев и ошибок в течение как можно большего непрерывного промежутка времени. Модули памяти класса PC Registered DIMM разработаны специально для обеспечения максимальной отказоустойчивости подсистемы памяти. Кроме этого они предоставляют два отдельных режима функционирования, оптимизации доступа к микросхемам памяти и выполнения операций, речь о которых пойдет далее.

Вся последующая информация, касающаяся топологии печатной платы (PCB Printed Circuit Board), а также рекомендаций и требований по разводке PCB, является базовой и может быть применена при рассмотрении не только конкретных типов модулей памяти, а и любых периферийных устройств, работающих на больших частотах общая разница минимальна. Отличия во временных параметрах, отдельных монтируемых компонентах (типа специфических микросхем), используемых конкретных топологических схемах и геометрии сигнальных линий исключительно численные и зависят от типа устройства и схемы согласования, применяемых в данных модулях памяти.

В настоящей статье довольно подробно описаны как основные отличительные особенности модулей памяти типа Registered DIMM, так и требования к разводке сигнальных трасс на печатной плате, включая узкоспециализированную информацию о монтируемых компонентах, которая может быть полезна для более детального ознакомления со спецификацией. Кажущуюся на первый взгляд слишком специфической информацию просто необходимо дать, чтобы (по мере возможности) отпали многочисленные возникающие вопросы о нестабильности работы как модулей памяти в целом, так и вообще устройств. Важно, чтобы читатель понял сложность разработки и реализации конечных продуктов такого уровня, как описываемые далее модули Registered DIMM, что поможет сузить в некоторых случаях круг поиска либо необходимого оборудования, либо причины возможных проблем неисправности или нестабильного функционирования. Таким образом, данный материал, думается, будет интересен самым широким слоям пользователей: либо уже столкнувшимся с определенными проблемами, либо желающим разобраться (на абсолютно разном уровне) и узнать больше об описываемых ниже модулях памяти, либо для тех, кто еще не остановил свой выбор на необходимом продукте данного класса и занимается постоянным поиском.SDRAM Registered DIMM, как концепция Registered DIMM

Модули 168pin, 3.3V, 72bit ECC SDRAM Registered DIMM (в дальнейшем SDRAM Registered DIMM, поскольку схема ECC принята за своего рода стандарт де-факто в данных модулях) в отличие от обычных обычных SDRAM DIMM имеют усовершенствованный механизм функционирования, обеспечивающий их гарантированную работу на частоте 100 MГц. Сама спецификация РС100 разработана именно для производства памяти, работающей на частоте 100 MГц, и использует технологию, применяющуюся при производстве пакетно-конвейерной кэш-памяти, что дает возможность уменьшить время запроса/вывода данных на шине с 10 нс до 8 нс, т.е. даже меньше, чем длительность периода тактовой частоты 100 MГц шины (tCK=10 нс).

Геометрия печатной платы Registered DIMM полностью соответствует требованиям, предъявляемым в рамках стандарта ANSI Y14.5M-1994, который сертифицирован для стандартных модулей класса Unbuffered/Buffered SDRAM DIMM.

| Габаритные размеры PCB Registered DIMM | ||||

| Габарит | Минимальный | Типичный | Максимальный | |

| Длина печатной платы модуля, мм | 133.22 | 133.37 | 133.52 | |

| Высота печатной платы модуля, мм | 38.12 | 43.18 | ||

| Толщина печатной платы модуля, мм | 1.17 | 1.27 | 1.37 | |

| Толщина модуля, включая монтаж микросхем, мм | 8.13 | |||

| Высота сигнального вывода, мм | 1.95 | 2.40 | 2.65 | |

| Ширина сигнального вывода, мм | 0.95 | 1.00 | 1.05 | |

| Расстояние между соседними сигнальными выводами, мм | 0.22 | |||

| Ширина механического ключа, мм | 2.00 ±0.10 mm | |||

| Примечание: | согласно ANSI Y14.5M-1994, расхождение не должно превышать ±0.13 от указанного размера | |||

Схемотехнически модуль SDRAM Registered DIMM, кроме микросхем памяти и, обязательно, микросхемы последовательного детектирования (SPD Serial Presence Detect), содержит и другие компоненты. Во-первых, это 18 бит 1:1 микросхемы-регистры (Register) типа 16835 или 162835 (с внутренними демпфирующими резисторами, сглаживающими «выбросы», обуславливаемые влияниями паразитных емкостей и индуктивностей, Internal Damping Resistor), обеспечивающих страничную организацию памяти. Во-вторых микросхема PLL (Phase Locked Loop) типа 2509 (1:9) и 2510 (1:10) фазовой автоподстройки частоты (ФАПЧ) с обратной связью (автоматическая регулировка) для задания и точного удержания необходимого значения частоты. Некоторые конфигурации позволяют не использовать микросхему ФАПЧ Non PLL Implementation. Микросхемы серии Register 16835/162836 и PLL 2509/2510 рекомендуются к применению, однако могут заменяться на эквивалентные.

Микросхемы-регистры играют роль транзитных буферов, перераспределяя адреса, и применяются для трансляции команд с их последующей передачей в микросхему памяти с задержкой в 1 такт. Тем не менее, данное +1T пенальти обычно включается в общий цикл ожидания контроллера памяти, обслуживающего Registered DIMM, поэтому в конечном итоге не выполняется никаких фаз дополнительно вводимой задержки. Микросхема PLL значительно уменьшает нагрузку на систему синхронизации, а устройства Register на командно-адресные сигнальные линии, что в результате позволяет использовать до 36 микросхем памяти на полную физическую строку (две физические строки или полный банк). Стандартно, микросхемы SDRAM имеют параллельную схему включения, что суммарно увеличивает потребляемый ток всеми устройствами, кроме чего не имеют возможности самоуправления (отключения) командно-адресного интерфейса. Буферные регистры наоборот обладают интерфейсом отключения входов, поэтому в состоянии деактивации ток утечки отсутствует.

Полная спецификация на модули SDRAM Registered DIMM указана в документах JESD21-C-4.5.7 и JESD JC-40, и все требования, описанные в рамках этих технических документов, должны строго выполняться сторонними разработчиками. Схемотехнические модификации не запрещаются, однако требуют жесткого согласования с требованиями, определяемыми рамками стандартов в части, касающейся сигнального интерфейса для выполнения обязательной тайминговой программы поддержки коммутаций 66/100 MГц (два специфических режима функционирования модулей Registered DIMM). После введения некоторых модификаций по оптимизации нагрузок на основные линии или маршрута прохождения сигнала (трассировка), разработанная схема должна подвергнуться тщательному анализу на специальных симуляторах и пройти лабораторные проверки по обеспечению выполнения основных требований касательно целостности сигнала и дальнейшего гарантированного четкого функционирования.

Конфигураций (модификаций) модулей памяти SDRAM Registered DIMM, описываемых в рамках упоминавшихся ранее стандартов, в виду специфичности применения существует довольно мало. Они характеризуются четкой схемой использования компонентов, что сказывается на общем объеме модуля памяти (несколько модификаций модулей объема 64, 128, 256, 512 и 1024 Mбайт) и нагрузке на основные сигнальные линии. Количество строк (# Rows of SDRAM) определяет нагрузку на линию RAS# и прямо указывает количество физических банков (1 или 2), занимаемых одним модулем в системе. Количество логических банков (# Banks in SDRAM) определяет архитектуру используемой микросхемы памяти и характеризует количество внутренних банков (в микросхемах SDRAM они «независимы» используют собственные для каждого банка усилители, формирователи сигналов и другую логику), определяющих количество массивов ячеек и объем памяти микросхемы.

Идентификация модуля системой происходит, как обычно, при помощи схемы последовательного детектирования (SPD), оговоренной в рамках JESD21C-4.1-R91. Ключевыми моментами в карте программирования EEPROM для корректного распознавания модуля SDRAM Registered DIMM и его функционирования являются байты: 2, 3, 4, 5, 6, 7, 8, 11, 13, 14, 21, 126 и 127 (см. пример карты программирования).

Рассмотрим подробнее особенности функционирования в системе модуля. Схема синхронизации SDRAM Registered DIMM выглядит следующим образом. От внешнего системного тактового генератора (CK97/CK98 или его эквивалента) синхросигналы поступают непосредственно на микросхему ФАПЧ, имеющую петлю обратной связи (с емкостью в цепи ОС для уменьшения фазовых ошибок) для подавления возможной девиации входящего тактового сигнала. Микросхема PLL коммутирует тактовые сигналы отдельно для микросхем SDRAM и Register с умышленным перекосом в 250 пс для обеспечения поступления большего количества адресов и увеличения длительности подготовки контрольных сигналов через микросхему Register на микросхемы SDRAM. Дополнительный перекос синхросигналов на микросхемы SDRAM и Register (±50 пс) обусловлен разностью длин сигнальных трасс к данным микросхемам на PCB. Фазовое отношение между системным синхросигналом и входным тактовым сигналом ФАПЧ является системозависимым. Кроме этого, вводится умышленный перекос 2.14 нс (±0.41нс) на тактовом входе (PCLKIN) контроллеров памяти базовых логик (например, FW82443BX или FW82443GX) от системного тактового синтезатора для совместимости с сигнальным протоколом PC100 SDRAM Unbuffered DIMM, согласно JESD21C-4.5.4-R9, чтобы была возможность использования в системе «разноплановых» модулей памяти.

Поэтому, протокол синхросигналов SDRAM Registered DIMM одной тактовой частоты и линией опорного напряжения (VREF = 1.4V) выглядит следующим образом. После коммутации, синхросигнал появляется на микросхемах Register, затем, после задержки в 250 пс, синхросигналы от системного тактового генератора появляются одновременно (с сигналом с PLL) на DIMM и входах микросхем SDRAM, а еще через 2140 пс синхросигнал появляется на входе контроллера памяти базовой логики. Здесь нужно учесть, что для тактовых сигналов системы (вход PCLKIN), микросхем SDRAM, Register и PLL опорным является передний фронт импульса синхросигнала на входе микросхемы ФАПЧ. Все умышленные задержки и выравнивание фазы контролируются емкостями и/или длинами сигнальных трасс.

Сигнал REGE подается на микросхему Register совместно с напряжением VDD через резистивную развязку и инвертирующий элемент. Именно этот сигнал и определяет один из двух режимов функционирования модуля: режим Buffered работает только при 15 нс тактовом импульсе (66.67 MГц), а режим Registered только при частоте шины 100 MГц (10 нс период).

Умышленно вводимый запас времени (Margin) для режима Buffered получается из тайминговых параметров режима Registered. Для полностью завершенных систем с высоким уровнем анализа таймингов, разработчик должен складывать/вычитать с/из этим запасом времени другие параметры. К последним относятся: время распространения сигнала от контроллера памяти до разъема DIMM (tSF System to DIMM Flight Time), перекос сигнала (Clock Skew), случайные выбросы (Clock Jitter), синхронизация внешнего регистра с задержкой на выходе (External Register Clock to Output Delay) и т.д. Тайминги в режиме Registered крайне критичны, а в режиме Buffered представляются на основе анализа таймингов режима Registered.

Схемотехника модулей SDRAM Registered DIMM основывается на обычной схеме построения ECC-модулей (72bit), одно- и двухстрочной организации, и предусматривает использование х4 (иногда х8, но ограничения по нагрузке на линиях DQ[63:0], DQMB[7:0], WE# и S[3:0]# должны быть рассчитаны дополнительно) микросхем SDRAM, полностью отвечающих стандарту РС100, прошедших тестирование в специальных условия.

Компоненты (микросхемы памяти, PLL и микросхемы-регистры) монтируются с одной (Single Side) и с двух сторон (Double Side) печатной платы, позиционируясь друг относительно друга, исходя из требований, предъявляемых к распределению монтажных мест и разводке трасс. Емкостные и резистивные развязки для микросхем SDRAM должны монтироваться в непосредственной близости от энергетических выводов один из способов уменьшения влияния дифференциальной формы ЭМИ (электромагнитной интерференции), возникающей вокруг сигнальных трасс в виде токовых петель. Двухрядная, двухсторонняя организация модулей, называемая Stacked, схемотехнически реализуется или планарно в два ряда, или использует накладной монтаж микросхем памяти друг на друга (IC-Tower), имеющих специальную цоколевку для конфигураций высокой плотностью расположения (Stacked SDRAM). Схема Stacked DIMM предполагает размещение на одном модуле 36 микросхем памяти, что при общей 64bit (+8 bit ECC) шине данных возможно только при использовании микросхем памяти организации х4, занимает две физические строки (полный банк) и определяет максимальную нагрузку на линии DQ[63:0], DQMB[7:0], WE# и S[3:0]#. В этом случае сигналы выбора кристалла CS#[1:0] и разрешения синхронизации CKE[1:0] имеют коммутируемые назначения: первая копия этих сигналов (CS0# и CKE0) управляет нижним рядом, а вторая (CS1# и CKE1) верхним.

Сигнальный интерфейс модулей SDRAM Registered DIMM предусматривает семь сигнальных категорий, разбитых по принципам особенностей топологической реализации.

| Сигнальные категории модуля SDRAM Registered DIMM | |||

| Сигнальная группа | Сигнал | Сигнальная группа | Сигнал |

| Синхронизация | CK[3:0] | Выбор кристалла | S[3:0]# |

| Данные | DQ[63:0], CB[7:0] | Разрешение синхронизации | CKE[1:0] |

| Маскирование данных, 1 | DQMB [0,2,3,4,6,7] | Адресация и контроль | A[13:0], BA[0,1], RAS#, CAS#, WE# |

| Маскирование данных, 2 | DQMB [1,5] | ||

Исходя из правил схемотехнической реализации модулей, основанной на особенностях интерфейса микросхем Register и PLL, а также учитывая их электрические параметры и внешние ограничения по нагрузке, разработаны схемотехнические рекомендации (базовый дизайн) SDRAM Registered DIMM для разных конфигураций.

Так, для 64 Мбайт Unstacked-модулей SDRAM Registered DIMM и для модулей, использующих 18 микросхем SDRAM (128, 256 и 512 Мбайт), используется две микросхемы Register. Для Stacked-модулей SDRAM Registered DIMM, использующих 36 микросхем SDRAM (256, 512 и 1024 Мбайт) три микросхемы Register.

Общее правило распределения нагрузки на выходах микросхемы PLL такое: четыре микросхемы SDRAM на один выход OUTх микросхемы ФАПЧ (сигнал PCLK). Последний выход OUTn остается зарезервированным для создания петли обратной связи, назначение которой описывалось ранее, со входом FDBK (FeeDBacK) микросхемы фазовой автоподстройки частоты.

| Использование микросхем Register в модулях SDRAM Registered DIMM | ||||

| Модуль DIMM | Номер Register | Количество Register | Емкость, Мбайт | |

| Stacked DIMM | с микросхемой PLL | 162835 | 3 | 256/512/1024 |

| Unstacked DIMM | с микросхемой PLL | 16835 | 2 | 128/256/512 |

| 64 Mбайт DIMM | с микросхемой PLL | 162835 | 2 | 64 |

| 64 Mбайт DIMM | без микросхемы PLL | 162835 | 2 | 64 |

Топологическая схема PCB модулей SDRAM Registered DIMM предусматривает соответствие материала печатной платы требованиям материалов электронной техники UL-94V-0 (текстолит), задержку распространения по внутренним слоям (Soi) 2.0-2.2 нс/фут, задержку распространения по внешним слоям (Sou) 1.6-2.2 нс/фут, полное сопротивление трассы (Zo) 58.5–71.5 Ом, шестислойную схему 4mil типа S-G-S-S-P-S при топологическом интервале 2.9-4-2.8-4-2.9 mils или шестислойную схему 6mil типа S-G-S-S-P-S при топологическом интервале 1.8-2.6-8.2-2.6-1.8 mils, где mil=0.0025 см. Плата должна иметь в основе полностью заполненные по площади сечения модуля энергетический (P) и экранирующий (G) слои, и выполняться согласно одной из двух уже просчитанных топологий (базовый дизайн), используя 4/6 mil ширину сигнальной трассы (слой S).

Дальнейшее развитие специфики Registered DIMM и увеличение частоты функционирования памяти дало толчок к появлению модулей PC133 SDRAM Registered DIMM, работающих соответственно на частоте 133 MГц. Однако в рамках основных документов спецификации JEDEC на модули этого класса соответствующих изменений произведено не было, что говорит о «узком круге» стандартизации в рамках отдельной спецификации, разработанной небольшой группой производителей и согласовано с разработчиками базовых логик (чипсетов). Поскольку общая схема согласования и топологических требований для каждой сигнальной группы известна, была сделана поправка на системные тайминги, регламентированные рамками требований открытой спецификации PC133: кроме использования микросхем памяти, гарантированно функционирующих на частоте 133 MГц, были сделаны поправки в модели согласования (сигнальная группа синхронизации CK[3:0] и CKE[1:0]), модификация и перерасчет топологии (остальные сигнальные группы) в следствие чего расширен базовый дизайн модуля и убран режим функционирования Buffered (на модулях PC133 SDRAM Registered DIMM линия REGE подтягивается до высокого уровня внешним резистором). Основной упор был, понятно, сделан на перерасчет таймингов PLL. Таким образом, новые модули PC133 SDRAM Registered DIMM предполагают модифицированный механизм функционирования исключительно в режиме Registered на частоте 133 MГц.

«Родственный» стандарт 184pin, 2.5V (SSTL_2), 64/72bit PC DDR SDRAM Registered DIMM, в отличие от ранее рассмотренного SDRAM Registered DIMM, разработан для применения в системах, поддерживающих технологию памяти DDR SDRAM, (PC200/PC266 с синхронизацией 100/133 MHz соответственно), оговоренную в рамках документа JEDEC JC-42.3-98-227A.

Основное отличие данного стандарта от рассматриваемого ранее на схемотехническом уровне заключается в том, что он поддерживает конфигурации как расширенной шины с поддержкой кода коррекции ошибок (72bit, 64bit+8bit ECC), так и стандартной (64bit). Модуль DDR SDRAM Registered DIMM основывается на SSTL_2-совместимом питающем протоколе (2.5V I/O, VDD=VDDQ=2.5V ±0.2V). Он содержит 13/14 bit микросхемы-регистры SSTL Register типа 1:2/1:1 соответственно, обеспечивающие страничную организацию памяти, и микросхему PLL (1:10), также функционирующую на SSTL-уровнях. Схемы распределения нагрузки на микросхемы Register и PLL несколько отличаются от описываемых ранее, использующихся в SDRAM Registered DIMM. Кроме данных компонент, некоторые конфигурации модулей включают еще и дополнительно коммутаторы на полевых транзисторах (FET-switches) основанных на схеме с открытым ненагруженным стоком (Open-Drain), применяющиеся для улучшения помехозащищенности проходящего сигнала и активизации соответствующих микросхем памяти.

По оснащенности вышеперечисленными компонентами, а также по базовому дизайну (об этом подробнее далее) модули DDR SDRAM Registered DIMM делятся на группы, спецификации на которые в последствии могут расширяться. DDR Registered DIMM модули с высокой плотностью размещения компонентов имеют монтаж микросхем памяти, отличающийся от применяемого в SDRAM Registered DIMM двухрядное расположение микросхем с обоих сторон печатной платы не используется, а применяется исключительно накладной монтаж IC-Tower.

В модулях DDR SDRAM Registered DIMM используют дифференциальный протокол синхронизации дифференциальные входные синхропары CK[1:0]/CK[1:0]# (позитивный сигнал/негативный «двойник») точка пересечения (средняя точка, уровень опорного напряжения) которых (по фронту CK[1:0]) являются опорной относительно поступления адресных и контрольных сигналов. Топология сигнальных трасс, временные протоколы и требования стандарта DDR SDRAM Registered DIMM отличаются лишь численно от общих требований Registered DIMM с упором на технологию DDR (обмен данными происходит по фронту и срезу (Both Edges) основных синхросигналов, CK[1:0]#). Как и в предыдущем случае, все требования, выдвигаемые для функционирования в режиме Registered с использованием микросхем Registered и PLL, четко оговорены в рамках документа JESD JC-40. Конфигурации модулей DDR SDRAM Registered DIMM объемом 64, 128, 256, 512, 1024 и 2048 Mбайт поддерживают микросхемы памяти емкостью 64, 128, 256 и 512 Mбит организации х4/х8 (Planar Components), применяющиеся для производства планарных модулей (Planar или Unstacked DIMM), и х4 высокой плотности упаковки (High Stack Package), использующихся при реализации модулей с высокой плотностью размещения компонентов (Stacked DIMM).

Цоколевка модуля DDR SDRAM Registered DIMM полностью соответствуют стандарту DDR SDRAM DIMM с/без ECC. Ранее отсутствовавший в спецификации SDRAM Registered DIMM асинхронный LVCMOS низкоуровневый сигнал RESET# применяется для гарантированного перевода выходов микросхемы Register в активное низкое состояние по требованию. Сигналы маскирования DM[8:0], имеющие высокий активный уровень, совместно с действующими входными данными DQ[63:0] имеют умышленно введенную однотактную задержку формирования после поступления команды записи. Фронт и срез сигналов DQS[8:0] применяются для стробирования приема/передачи данных непосредственно по линиям DQ[63:0]: в режиме передачи для считываемых данных, в режиме приема для записываемых, причем фронт и срез является командным для чтения данных, а середина строба для записи. Вывод FETEN является опциональным и используется в конфигурациях, имеющих коммутаторы на полевых транзисторах (группы F, H и K). Линии VDDSPD, VDDID и VDDQ выполняют соответственно функции питания микросхемы SPD (данный вывод должен быть изолирован от линий питания VDD и VDDQ), идентификационного флага напряжения VDD и питания линий данных. Уникальный сигнал REGE, осуществляющий переключение между двумя специфическими режимами функционирования, отсутствует в настоящем стандарте DDR SDRAM Registered DIMM, что говорит о функционировании исключительно в режиме Registered.

Идентификация модуля системой происходит, как обычно, при помощи схемы последовательного детектирования (см. пример карты программирования), оговоренной в рамках JEDEC ballot JC-42.5-5-99-102, описывающего стандарт стандарт SPD для DDR SDRAM Registered DIMM. Однако данное требование целиком опирается на основной стандарт последовательного детектирования, описываемый в упоминающемся ранее документе JESD21C-4.1-R91.

Габаритные размеры PCB DDR SDRAM Registered DIMM полностью соответствуют типоразмерам Registered DIMM, приводимым ранее. Топологическая схема предусматривает соответствие материала печатной платы требованиям UL-94V-0, задержку распространения по внутренним слоям (Soi) 2.0-2.2 нс/фут, задержку распространения по внешним слоям (Sou) 1.6-2.2 нс/фут, полное сопротивление трассы (Zo) 54-66 Ом и восьмислойную схему 4/6 mil типа S-G-P-S-S-P-G-S.

Общие требования по трассировке и расчету параметров модулей Registered DIMM сводятся к рассмотрению нескольких моментов в расчете топологии модуля и размещении связующих компонентов. Для стандартов SDRAM Registered DIMM и DDR SDRAM Registered DIMM данные требования и различия носят численный характер, поэтому конечный производитель должен учитывать настоящие рекомендации. Рассмотрим требования для DDR SDRAM Registered DIMM.

Задержка подачи управляющих синхросигналов к микросхемам памяти на модуле оптимизирована для высокоскоростных операций на уровне топологии и трассировки печатной платы. Полная задержка поступления синхросигнала складывается из времени задержки распространения от интерфейса модуля до входных выводов микросхемы PLL, времени задержки распространения по сигнальной трассе от микросхемы ФАПЧ до микросхемы SDRAM и задержки «pin-pin» на пассивных компонентах типа серий резисторов. Эта суммарная задержка рассчитывается и моделируется непосредственно производителем модуля согласно общей спецификации и требованиям к тайминговой программе конкретной сигнальной группы. Иными словами, предлагается конкретная базовая модель с точно рассчитанными параметрами (Reference Net, например, в случае DDR SDRAM Registered DIMM семь модификаций A, B, C, E, F, H и K), имеющая конкретную топологию, изменяя которую добиваются оптимизации согласования по таймингам и маршрута сигналов, однако установленные временные и нагрузочные параметры остаются постоянными.

Изначально, номинальная задержка распространения сигнала от входа PLL до входа соответствующей микросхемы принята за 0 пс. Промежуток подачи синхросигнала на вход микросхемы ФАПЧ не должен регулироваться источниками вариаций временных параметров, включающих входную емкость PLL, допустимые отклонения номиналов использующихся резисторов и емкостных характеристик выводов, а также импедансных вариаций (изменение полного сопротивления), которые могут давать эффект. Однако, реализуя эти вариации, можно изменять и контролировать задержку в промежутке ±100 пс на рассматриваемом участке.

Наиболее важный фактор, влияющий на параметры опорного синхросигнала это обеспечение четко рассчитанного промежутка поступления синхросигнала на микросхему памяти. Базовый дизайн модуля памяти предполагает заранее рассчитанную сеть параметров со стандартными задержками. Конкретный производитель конечного модуля может изменять эти параметры в пределах ранее указываемого промежутка (±100 пс) при помощи петли обратной связи в цепи микросхемы PLL, учитывая возможные «всплески». Данное значение не включается в крайний результат «погрешности» временного перекоса на PLL, возникновения фазовой ошибки и отклонения от номинала конденсатора в цепи ОС.

Непосредственно синхросигнал, поступающий на микросхему Register, должен совпадать по фазе с синхросигналом микросхем памяти с возможностью отклонения в определенные ранее ±100 пс. Фактическая же задержка может варьироваться и зависит от входной емкости микросхем памяти, входной емкости микросхемы Register, перекоса на выходе PLL, обусловленного паразитными наводками на РСВ, и уже конкретно топологическими отклонениями, вызванными несовершенностью технологии изготовления и имеющих вторичный эффект. В случае прихода синхросигнала на вход микросхемы Register раньше, чем синхросигнала на вход микросхем памяти, синфазность можно исправить увеличением в цепи микросхемы-регистра номинала сопрягающего (выравнивающего) конденсатора (Clock Padding Capacitor), компенсирующего временной сдвиг между сигналами, затягивая фронт и срез тактового импульса.

Все вносимые изменения в базовую модель требуют тщательной перепроверки новой модели. Моделирование позволяет непосредственно каждому производителю модуля памяти добиваться комбинированием параметров номинального 0ps отношения между входящим синхросигналом микросхем Register и микросхем памяти (синфазность). Данное условие довольно критично и его анализ позволяет рассчитывать и точно удерживать требуемые характеристики, составляющие такой параметр, как целостность сигнала (Signal Integrity) на входах микросхем памяти и Register. Например, там где «регистровые» синхросигналы не «вмещаются» в идеальное тайминговое окно (четкое совпадение соответствующих значений на конкретном участке), не менее критичные пост-регистровые тайминги необходимо корректировать для обеспечения четкого выполнения операций и гарантированного функционирования модуля, а также устранения возникновения возможных «плывущих» таймингов (рассредоточение временных параметров).

Итак, после краткого технического экскурса становится очевидным область применения модулей Registered DIMM это, конечно же, системы с максимальной степенью отказоустойчивости (например, сервера), базирующиеся, на логических наборах, поддерживающих модули PC Registered DIMM. Например, SDRAM Registered DIMM поддерживается наборами i82440BX и i82440GX производства Intel и логиками ServerWorks ServerSet III xE производства ServerWorks, а модули DDR SDRAM Registered DIMM чипсетами AMD-760MP и AMD-760MPX. Для такого заключения есть абсолютно все основания: наличие на модуле отдельной реализации фазовой автоподстройки частоты с обратной связью (PLL) для стабилизации протокола группы синхросигналов и уменьшения нагрузки на сигнальные линии, 72bit организация модуля с кодом коррекции ошибок (ECC) для выделения и устранения возможных ошибок, наличие специализированной микросхемы страничной адресации (Registered), плюс, схемотехнически индивидуальный подход с некоторыми собственными правилами разводки и монтажа требования для «встречного» согласования по временным параметрам и минимизации влияния ЭМИ.

Необходимо заметить, что, поскольку модуль памяти Registered DIMM является довольно специфическим устройством с особенностями функционирования, далеко не каждый логический набор (чипсет) поддерживает эту разновидность модулей синхронного ДОЗУ. Производитель материнской платы, использующий такой чипсет, обязан предоставить список вендоров (конечных производителей), модули памяти которых успешно прошли тестирование на данной платформе. Поэтому для компоновки конечной системы следует подбирать модули памяти согласно предлагаемого списка производителя платформы сертифицированных модулей памяти. Справедливости ради надо также заметить, что некоторые производители материнских плат полностью исключают поддержку модулей, отличных от Registered DIMM (в такой системе обычные модули Unbuffered DIMM функционировать не будут), поэтому необходимо внимательно изучать спецификацию желаемой платформы.