Что такое ssse3 в процессоре

SSSE3

Supplemental Streaming SIMD Extension 3 (SSSE3) — это обозначение данное Intel’ом четвёртому расширению системы команд. Предыдущее имело обозначение SSE3 и Intel добавил ещё один символ ‘S’ вместо того, чтобы увеличить номер расширения, возможно потому, что они посчитали SSSE3 простым дополнением к SSE3. Часто, до того как стало использоваться официальное обозначение SSSE3, эти новые команды назывались SSE4. Также их называли кодовыми именами Tejas New Instructions (TNI) и Merom New Instructions (MNI) по названию процессоров, где впервые Intel намеревалась поддержать эти новые команды. Появившись в Intel Core Microarchitecture, SSSE3 доступно в сериях процессоров Xeon 5100 (Server и Workstation версии), а также в процессорах Intel Core 2 (Notebook и Desktop версии) и Intel Atom.

Новыми в SSSE3, по сравнению с SSE3, являются 16 уникальных команд, работающих с упакованными целыми. Каждая из них может работать как с 64-х битными (MMX), так и с 128-ми битными (XMM) регистрами, поэтому Intel в своих материалах ссылается на 32 новые команды.

Содержание

Новые инструкции

Работа со знаком

Каждое поле результата есть абсолютная величина соответствующего поля из src1. Фактически это те же операции PSIGNB, PSIGNH, PSIGNW у которых оба аргумента один и тот же регистр.

Каждое поле результата есть произведение поля из src1 на <-1,0,1>в зависимости от знака соответствующего поля в src2 (умножение на 0 когда поле в src2 равно нулю).

Сдвиги

Два регистра операнда рассматривается как одно беззнаковое промежуточное значение удвоенной размерности из которого извлекается 64-х/128-х битное значение начиная с байта указанного в непосредственном аргументе-константе команды.

Перемешивание байт

Перестановка байт, каждый байт результата есть некоторый байт из первого аргумента определяемый по соответствующему байту из второго аргумента (если байт отрицательный, то в байт результат прописывается ноль, иначе используются младшие 3 или 4 бита как номер байта в первом аргументе).

Умножения

Аргументы A и B рассматриваются как вектора 16-ти битных знаковых чисел с фиксированной запятой представленных в диапазоне [-1,+1) (то есть 0x4000 это 0.5, а 0xa000 это −0.75 и т. д.), которые перемножаются друг с другом с корректным округлением.

Производится побайтное перемножение векторов A и B, промежуточные 16-ти битные результаты попарно складываются между собой с насыщением и выдаются как результат.

Горизонтальные сложения/вычитания целых

Горизонтальное вычитание целых 16/32 битных полей.

Горизонтальное вычитание целых 16 битных полей с насыщением.

Горизонтальное сложение целых 16/32 битных полей.

Горизонтальное сложение целых 16 битных полей с насыщением.

Процессоры, поддерживающие SSSE3

Литература

| Наборы расширения базовых инструкций процессоров семейства x86 |

|---|

| MMX | MMXEXT | SSE | SSE2 | SSE3 | SSSE3 | SSE4 | ATA | 3DNow! | 3DNowExt | SSE5 | AVX | AES |

Полезное

Смотреть что такое «SSSE3» в других словарях:

SSSE3 — (Supplemental Streaming SIMD Extensions 3) bezeichnet die mit Intels Core Architektur eingeführten Erweiterungen des SSE3 Befehlssatzes. Firmenintern werden auch die Bezeichnungen „Tejas New Instructions“ (TNI) oder „Merom New Instructions“ (MNI) … Deutsch Wikipedia

SSSE3 — Saltar a navegación, búsqueda Supplemental Streaming SIMD Extension 3 son una mejora menor de las extensiones SSE3 ya introducidas anteriormente en la linea Prescott, fue presentada en los procesadores Intel Core 2 Duo y Xeon. Fueron agregadas 32 … Wikipedia Español

SSSE3 — Supplemental Streaming SIMD Extension 3 (SSSE3) aussi connu sous le nom de code Tejas New Instructions (TNI) est le quatrième jeu d instruction SSE, souvent nommé à tort SSE4. Introduit par Intel dans son architecture Core, le jeu d instruction… … Wikipédia en Français

SSSE3 — Supplemental Streaming SIMD Extension 3 (SSSE3) is Intel s name for the SSE instruction set s fourth iteration. The previous version was SSE3, and Intel have added an S rather than increment the version number, as they appear to consider it… … Wikipedia

Supplemental Streaming SIMD Extension 3 — SSSE3 Supplemental Streaming SIMD Extension 3 (SSSE3) aussi connu sous le nom de code Tejas New Instructions (TNI) est le quatrième jeu d instruction SSE, souvent nommé à tort SSE4. Introduit par Intel dans son architecture Core, le jeu d… … Wikipédia en Français

Supplemental Streaming SIMD Extensions 3 — SSSE3 (Supplemental Streaming SIMD Extensions 3) bezeichnet die mit Intels Core Architektur eingeführten Erweiterungen des SSE3 Befehlssatzes. Firmenintern werden auch die Bezeichnungen „Tejas New Instructions“ (TNI) oder „Merom New Instructions“ … Deutsch Wikipedia

List of Intel Core 2 microprocessors — The Core 2 brand refers to Intel s x86/x86 64 microprocessors with the Core microarchitecture targeted at the consumer and business markets (except servers) above Pentium. The Core 2 solo branch covered single core CPUs for notebook computers,… … Wikipedia

Intel Core 2 Duo (Mobil) — Intel Core 2 Duo Intel Core 2 Duo Emblem Produktion: seit 2006 Produzent: Intel Prozessortakt: 1,06 GHz … Deutsch Wikipedia

Список микропроцессоров Intel — Информация в этой статье или некоторых её разделах устарела. Вы можете помочь проекту … Википедия

Intel Xeon (Core) — Intel Xeon >> Logo der Xeon Core Reihe Produktion: seit 2006 Produzent … Deutsch Wikipedia

Использование набора инструкций Intel SSSE3 для ускорения реализации алгоритма DNN в задачах распознавания речи, выполняемых на мобильных устройствах

За последние тридцать лет технологии распознавания речи серьёзно продвинулись вперед, начав свой путь в исследовательских лабораториях и дойдя до широкого круга потребителей. Эти технологии начинают играть важную роль в нашей жизни. Их можно встретить на рабочем месте, дома, в машине. Их используют в медицинских целях и в других сферах деятельности. Распознавание речи входит в топ-10 перспективных технологий мирового уровня.

Обзор

В результате исследований последних лет произошла смена основных алгоритмов распознавания речи. Так, прежде это были алгоритмы GMM (Gaussian Mixture Model) и HMM-GMM (Hidden Markov Model – Gaussian Mixture Model). От них произошёл переход к алгоритму DNN (Deep Neural Network). Работа этого алгоритма напоминает деятельность человеческого мозга. Здесь используются сложные вычисления и огромное количество данных.

Благодаря Интернету воспользоваться современными технологиями распознавания речи может любой владелец смартфона. К его услугам – бесчисленное множество серверов. А вот без Интернета службы распознавания речи в мобильных устройствах почти бесполезны. Они редко способны правильно понимать тех, кто пытается с ними «разговаривать».

Можно ли перенести реализацию алгоритма DNN с сервера на смартфон или планшет? Ответ на этот вопрос – да. Благодаря поддержке процессорами от Intel набора инструкций SSSE3, на мобильных устройствах можно пользоваться приложениями для распознавания речи, основанными на алгоритме DNN. При этом подключение к Интернету не требуется. В результате наших испытаний точность распознавания речи таким приложением составила более 80%. Это очень близко к тому, что достижимо при использовании серверных систем. В этом материале мы расскажем об алгоритме DNN и о том, как набор инструкций Intel SSSE3 способен помочь в ускорении расчётов, необходимых для реализации этого алгоритма.

Предварительные сведения

DNN (ГНС) – это сокращение от Deep Neural Network (Глубокая Нейронная Сеть). Это – сеть прямого распространения, содержащая множество скрытых слоёв. DNN находится на переднем крае современных технологий машинного обучения. Для этого алгоритма нашлось множество вариантов практического применения.

Глубокие нейронные сети имеют большое количество скрытых слоёв. При их обучении нужно модифицировать десятки миллионов параметров. Как результат, обучение таких сетей требует значительных затрат времени.

Распознавание речи – типичный пример применения DNN. Упрощённо, приложения для распознавания речи можно представить состоящими из акустической модели (acoustic model), языковой модель (language model) и подсистемы декодирования (decoding). Акустическая модель используется для моделирования распределения вероятностей вариантов произношения. Языковая модель применяется для моделирования связей между словами. На этапе декодирования используются две вышеописанные модели, речь преобразуется в текст. Нейронная сеть умеет моделировать любые словесные конструкции. В то время как глубокая нейронная сеть имеет более сильную способность к выделению существенных признаков данных, чем мелкая (shallow) сеть, она моделирует структуру человеческого мозга, и, таким образом, способна более точно «понять» характеристики вещей. В результате, в сравнении с другими методами, в такой нейронной сети можно более точно смоделировать акустические и языковые модели.

Области применения алгоритма DNN

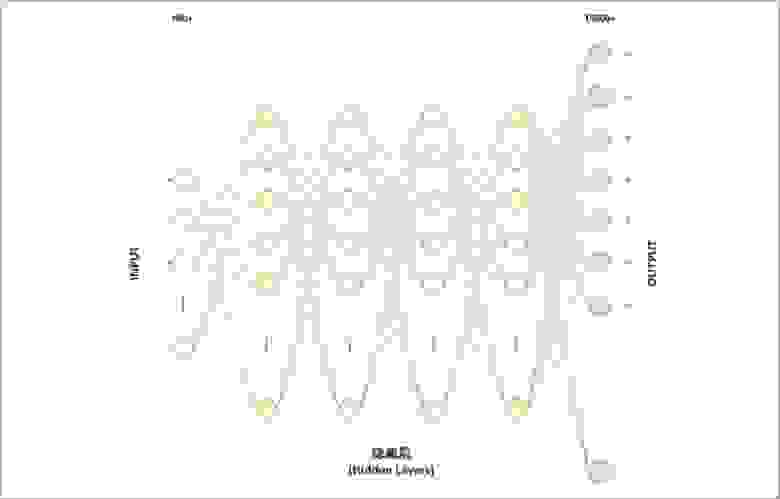

Схема типичной глубокой нейронной сети

Обычно типичная глубокая нейронная сеть содержит множество линейных и нелинейных слоёв, которые накладываются друг на друга.

Четыре скрытых слоя в акустической модели, построенной на базе DNN

Сеть, схема которой здесь приведена, состоит из набора линейных слоёв. Каждый нейрон из предыдущего слоя связан с каждым нейроном из следующего. Связь входа сети с её выходом можно описать следующей формулой:

X T – это вектор-строка, вход нейронной сети. В применении к распознаванию речи мы обычно помещаем 4 фрагмента данных для одновременной работы над ними, таким образом, создавая входную матрицу 4xM. W T и B это, соответственно, линейная матрица преобразования нейронной сети и вектор смещения. Обычно размерность такой сети очень велика, во всех слоях имеется одинаковое количество нейронов, то есть, сеть имеет квадратную форму.

Набор инструкций Intel SSSE3

Intel называет набор команд Supplemental Streaming SIMD Extensions 3, или, для краткости, просто SSSE3, расширением набора команд SSE3. Это – часть технологии SIMD, интегрированной в микропроцессоры Intel. Данная технология рассчитана на улучшение возможностей по обработке мультимедийных данных. Она предназначена для ускорения выполнения задач кодирования и декодирования информации и для ускорения проведения различных расчётов. Используя набор инструкций SSSE3, мы можем обрабатывать несколько потоков данных с помощью одной инструкции за один тактовый цикл. Это позволяет значительно повысить эффективность приложений. В частности, команды SSSE3 применимы к матричным вычислениям.

Для использования набора инструкций SSSE3 нужно подключить соответствующие заголовочные файлы SIMD:

Заголовочный файл tmmintrin.h обеспечивает работу с SSSE3, ниже приведено описание функций, которые в нём определены.

Определения структур данных __m64 и __m128 находятся в заголовочном файле для MMX (mmintrin.h) и SSE (xmmintrin.h).

Пример: использование функций SSSE3 для ускорения вычислений, примеряющихся в алгоритме DNN

Здесь мы рассмотрим пару функций. На их примере будет показано, как SSSE3 используется для ускорения расчётов при реализации алгоритма DNN.

__m128i _mm_maddubs_epi16 (__m128i a, __m128i b) Сложение с насыщением

Эта функция очень важна при выполнении матричных вычислений в алгоритме DNN. Параметр – это 128-битный регистр (register), который используется для хранения 16-ти целых чисел без знака (8-ми битных). Параметр b – это целое со знаком, тоже 8-ми битное. Возвращаемый результат – это 8 16-битных целых чисел со знаком. Эта функция отлично подходит для выполнения матричных вычислений:

__m128i _mm_hadd_epi32 (__m128i a, __m128i b) Сложение смежных элементов

Эту функцию можно назвать функцией, которая выполняет попарное сложение. Параметры a и b – это 128-битные регистры, которые хранят по 4 целых 32-битных числа со знаком. В соответствии с обычной операцией по сложению соответствующих элементов в двух векторах, команда выполняет сложение смежных элементов входного вектора:

Предположим, у нас есть задача вычислений на векторах, типичная для реализации DNN.

Имеются пять векторов: a1, b1, b2, b3, b4. Вектор a1 – это одномерный массив из 16-ти целых чисел типа signed char. Векторы b1, b2, b3, b4 – массивы целых чисел из 16 элементов каждый типа unsigned char. Нам нужно получить скалярные произведения a1*b1, a1*b2, a1*b3, a1*b4 результат надо сохранить в виде 32-битного целого числа со знаком.

Если мы воспользуемся обычным для программирования на C подходом, то код для решения этой задачи будет выглядеть так:

Предположим, что за один тактовый цикл можно выполнить одну операцию умножения и одну операцию сложения. Получаем – 64 тактовых цикла на выполнение расчётов.

Теперь воспользуемся набором инструкций SSSE3 для решений той же задачи.

Результат мы сохраняем в 128-битном регистре (с), в котором помещаются 4 целых числа. Учитывая конвейерную обработку данных, на вычисления уйдёт 12 или 13 тактовых циклов. Если сравнить эти данные, получится следующее: